Untuk alasan di atas ini kelompok peneliti Prof. Liu Yuan di Universitas Hunan, Tiongkok mengadopsi metode integrasi elektroda logam van der Waals berenergi rendah ubtuk mewujudkan perangkat vertikal saluran pendek dengan lapisan tipis atau bahkan satu lapisan atom molibdenum disulfida (MoS2) sebagai saluran semikonduktor.

Dengan menggunakan molibdenum disulfida (MoS2) sebagai lapisan tipis atau bahkan lapisan atom tunggal dari saluran semikonduktor, yang berarti panjang saluran sebenarnya adalah ketebalan lapisan bahan molibdenum disulfida, jadi disusun secara terpendek hingga dapat mencapai 0.65nm.

Dan transistor yang disusun secara vertikal tidak perlu menggunakan mesin litografi presisi tinggi untuk memperpendek jarak antar transistor, cukup disusun lapis demi lapis dengan gaya blok bangunan, itulah sebabnya mesin litografi presisi tinggi tidak diperlukan.

Dalam kenyataannya, para peneliti telah mengembangkan transistor efek medan vertikal semacam ini sejak lama. Universitas Hunan bukanlah yang pertama melakukan penelitian, tetapi di masa lalu, belum ada yang menemukan bahan yang ideal, sehingga transistor semacam ini akan terpengaruh oleh arus tunneling vertikal ketika disusun secara vertikal, akibatnya, selama di bawah 10nm, tidak dapat direalisasikan oleh pengaturan gerbang (gate).

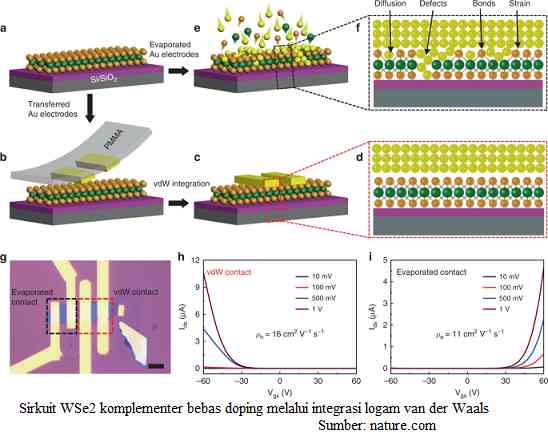

Para peneliti secara fisik melapisi elektroda logam prefabrikasi di atas saluran molibdenum disulfida, mempertahankan struktur kisi semikonduktor dua dimensi dan sifat intrinsiknya untuk membentuk interface/antarmuka logam-semikonduktor van der Waals yang ideal versus interface logam-semikonduktor yang dibentuk oleh logam konvensional.

Teknik dikedapankan dibandingkan dengan kerataan tingkat atom dari antarmuka ideal, arus tunneling berkurang dengan menskalakan perangkat vertikal, dalam pekerjaan ditemukan bahwa perangkat vertikal dengan panjang saluran 0,65nm dan 3,6nm masih dapat mencapai on- rasio off 26 dan 1000, dan kinerja rasio on-off transistor vertikal ditingkatkan dengan dua kali lipat.

Selain itu, uji kelistrikan suhu rendah menunjukkan bahwa mekanisme kerja perangkat vertikal van der Waals masih didominasi oleh emisi termionik di bawah saluran sangat pendek 3,6 nm.

Kali ini, tim Universitas Hunan menggunakan metode integrasi elektroda logam van der Waals untuk membentuk interface/antarmuka logam-semikonduktor van der Waals yang ideal dengan molibdenum disulfida (MoS2), dan baru kemudian dapat mencapai ketebalan 0,65 nm, sehingga membuat teknologi ini menjadi layak.

Dan selama ini diketahui bahwa dalam proses chip sebelumnya, panjang saluran mewakili proses chip, artinya, panjang saluran 0,65nm berarti proses chip 0,65nm.

Kita sudah tahu bahwa teknologi Tiongkok saat ini masih 14nm, dan TSMC masih 5nm. Tiba-tiba, Universitas Hunan telah mendapatkan lebih tinggi 0,65nm, ini sungguh sangat mengejutkan. Lebih penting lagi, peningkatan teknologi chip dalam pembuatan chip di masa lalu sangat bergantung pada keakuratan mesin litografi.

Misalnya, chip 7nm ke bawah memerlukan mesin litografi EUV, dan transistor efek medan pemrosesan Universitas Hunan tidak sepenuhnya bergantung pada mesin litografi presisi tinggi karena metode pengaturan yang berbeda.