Pada Juni 2021, tim Profesor Liu Yuan dari Departemen Fisika dan Mikroelektronika Universitas Hunan merealisasikan transistor efek medan vertikal saluran ultra-pendek dengan menggunakan metode integrasi logam van der Waals, yang memberikan ide baru untuk lebih meningkatkan kinerja perangkat semikonduktor.

Hasil penelitian dipublikasikan di Nature Electronic, jurnal elektronik, Departemen Fisika dan Mikroelektronika Universitas Hunan merupakan unit pertama, dan Profesor Liu Yuan adalah editor penulis dan Liu Liting seorang mahasiswa pascasarjana dari Departemen Fisika dan Mikroelektronika, adalah penulis pertama.

Dengan perkembangan kebutuhan perangkat berkinerja tinggi. Sesuai dengan upaya untuk melakukan penyusutan ukuran perangkat yang terus menerus merupakan tren yang tak terelakkan.

Hukum Moore menunjukkan bahwa jumlah perangkat elektronik yang terintegrasi pada chip sirkuit terintegrasi (IC) akan berlipat ganda setiap 18-24 bulan, dan kinerja perangkat mikroprosesor akan berlipat ganda atau harganya akan turun setengahnya.

Menurut Hukum Moore, node proses perangkat berkurang pada tingkat 0,7 kali. Namun, dalam beberapa tahun terakhir, Hukum Moore mulai goyah. Karena perangkat diminiaturkan ke skala nano, mobilitas transistor dimulai menurun, arus bocor terus meningkat, dan konsumsi daya meningkat dan efek saluran pendek parah lainnya.

Hal ini membawa pendekatan penskalaan transistor paralel tradisional mendekati batas fisik sudah "mentok". Untuk lebih mempromosikan miniaturisasi transistor, pengembangan perangkat dengan struktur baru telah membangkitkan minat banyak peneliti.

Transistor vertikal memiliki karakteristik saluran pendek alami, dan panjang saluran hanya ditentukan oleh ketebalan material. Semikonduktor cukup ditempatkan di antara elektroda bawah dalam struktur sandwich. Oleh karena itu, penelitian dan pengembangan transistor vertikal diharapkan dapat menjadi arah penskalaan perangkat baru, yang dapat mengurangi saluran panjang fisik saluran dikurangi menjadi di bawah 10nm atau bahkan 5nm. Alih-alih untuk menghindari atau mengandalkan mesin fotolitografi presisi tinggi tradisional.

Namun, di bawah pengaruh teknologi pengendapan logam berenergi tinggi tradisional, interface/antarmuka kontak yang sangat tidak memuaskan terbentuk antara semikonduktor logam dari transistor vertikal, yang akan menghancurkan saluran seluruh perangkat dan meningkatkan arus tunneling vertikal sehingga perangkat tidak dikendalikan oleh gerbang (gate)

Fenomena ini lebih jelas pada perangkat saluran pendek, membuat penskalaan perangkat vertikal di bawah 10 nm menjadi tantangan besar.

Sederhananya, transistor tidak disusun secara paralel, melainkan vertikal. Struktur vertikal ini memiliki karakteristik saluran alami, dan panjang saluran antara elektroda bawah dan elektroda atas hanya bergantung pada ketebalan material.

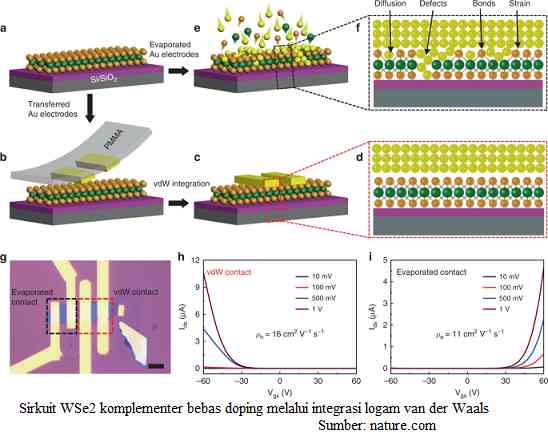

Untuk alasan di atas ini kelompok peneliti Prof. Liu Yuan di Universitas Hunan, Tiongkok mengadopsi metode integrasi elektroda logam van der Waals berenergi rendah ubtuk mewujudkan perangkat vertikal saluran pendek dengan lapisan tipis atau bahkan satu lapisan atom molibdenum disulfida (MoS2) sebagai saluran semikonduktor.

Dengan menggunakan molibdenum disulfida (MoS2) sebagai lapisan tipis atau bahkan lapisan atom tunggal dari saluran semikonduktor, yang berarti panjang saluran sebenarnya adalah ketebalan lapisan bahan molibdenum disulfida, jadi disusun secara terpendek hingga dapat mencapai 0.65nm.

Dan transistor yang disusun secara vertikal tidak perlu menggunakan mesin litografi presisi tinggi untuk memperpendek jarak antar transistor, cukup disusun lapis demi lapis dengan gaya blok bangunan, itulah sebabnya mesin litografi presisi tinggi tidak diperlukan.

Dalam kenyataannya, para peneliti telah mengembangkan transistor efek medan vertikal semacam ini sejak lama. Universitas Hunan bukanlah yang pertama melakukan penelitian, tetapi di masa lalu, belum ada yang menemukan bahan yang ideal, sehingga transistor semacam ini akan terpengaruh oleh arus tunneling vertikal ketika disusun secara vertikal, akibatnya, selama di bawah 10nm, tidak dapat direalisasikan oleh pengaturan gerbang (gate).

Para peneliti secara fisik melapisi elektroda logam prefabrikasi di atas saluran molibdenum disulfida, mempertahankan struktur kisi semikonduktor dua dimensi dan sifat intrinsiknya untuk membentuk interface/antarmuka logam-semikonduktor van der Waals yang ideal versus interface logam-semikonduktor yang dibentuk oleh logam konvensional.

Teknik dikedapankan dibandingkan dengan kerataan tingkat atom dari antarmuka ideal, arus tunneling berkurang dengan menskalakan perangkat vertikal, dalam pekerjaan ditemukan bahwa perangkat vertikal dengan panjang saluran 0,65nm dan 3,6nm masih dapat mencapai on- rasio off 26 dan 1000, dan kinerja rasio on-off transistor vertikal ditingkatkan dengan dua kali lipat.

Selain itu, uji kelistrikan suhu rendah menunjukkan bahwa mekanisme kerja perangkat vertikal van der Waals masih didominasi oleh emisi termionik di bawah saluran sangat pendek 3,6 nm.

Kali ini, tim Universitas Hunan menggunakan metode integrasi elektroda logam van der Waals untuk membentuk interface/antarmuka logam-semikonduktor van der Waals yang ideal dengan molibdenum disulfida (MoS2), dan baru kemudian dapat mencapai ketebalan 0,65 nm, sehingga membuat teknologi ini menjadi layak.

Dan selama ini diketahui bahwa dalam proses chip sebelumnya, panjang saluran mewakili proses chip, artinya, panjang saluran 0,65nm berarti proses chip 0,65nm.

Kita sudah tahu bahwa teknologi Tiongkok saat ini masih 14nm, dan TSMC masih 5nm. Tiba-tiba, Universitas Hunan telah mendapatkan lebih tinggi 0,65nm, ini sungguh sangat mengejutkan. Lebih penting lagi, peningkatan teknologi chip dalam pembuatan chip di masa lalu sangat bergantung pada keakuratan mesin litografi.

Misalnya, chip 7nm ke bawah memerlukan mesin litografi EUV, dan transistor efek medan pemrosesan Universitas Hunan tidak sepenuhnya bergantung pada mesin litografi presisi tinggi karena metode pengaturan yang berbeda.

Mengingat Tiongkok hingga kini sama sekali tidak bisa membeli mesin litografi EUV, dan presisi mesin litografi Tiongkok yang ada masih 90nm.

Jadi apa prinsip dari teknologi ini?

Untuk membicarakan tentang komposisi chip di masa lalu. Kita tahu bahwa chip terdiri dari transistor, dan transistor disusun secara paralel di dalam chip. Oleh karena itu, meningkatkan proses pembuatan chip sebenarnya mengurangi jarak antar transistor dan ukuran transistor .

Untuk tujuan ini membutuhkan penggunaan mesin litografi presisi tinggi, dan tim Universitas Hunan sedang meneliti teknologi lain, yaitu transistor efek medan vertikal.

Perlu diketahui penyusunan Transistor vertikal: di mana panjang saluran ditentukan oleh ketebalan semikonduktor --- menarik dalam pengembangan perangkat elektronik generasi mendatang.

Dan transistor yang disusun secara vertikal tidak perlu menggunakan mesin litografi presisi tinggi untuk memperpendek jarak antar transistor, cukup disusun lapis demi lapis dengan gaya blok bangunan, itulah sebabnya mesin litografi presisi tinggi tidak diperlukan.

Kali ini, tim Universitas Hunan membentuk antarmuka logam-semikonduktor van der Waals yang ideal dengan molibdenum disulfida (MoS2) menggunakan metode integrasi elektroda logam van der Waals, dan mencapai ketebalan 0,65 nm, membuat teknologi ini menjadi layak.

Namun, perangkat vertikal saluran pendek sulit dibuat, karena proses metalisasi energi tinggi biasanya mengakibatkan kerusakan pada daerah kontak. Di sini dapat menunjukkan bahwa transistor vertikal molibdenum disulfida (MoS2) dengan panjang saluran hingga satu lapisan atom dapat dibuat menggunakan teknik integrasi logam van der Waals berenergi rendah.

Pendekatan ini menggunakan elektroda logam prefabrikasi yang dilaminasi secara mekanis dan ditransfer di atas heterostruktur vertikal MoS2/graphene, yang mengarah ke transistor efek medan vertikal dengan rasio on-off 26 dan 103 untuk panjang saluran masing-masing 0,65nm dan 3,60nm.

Dengan menggunakan pemindaian tunneling microscopy dan pengukuran listrik suhu rendah, dapat menunjukkan bahwa peningkatan kinerja listrik adalah hasil dari interface/antarmuka logam-semikonduktor berkualitas tinggi, dengan arus tunneling langsung yang diminimalkan dan efek penyematan level Fermi. Pendekatan ini juga dapat diperluas ke bahan berlapis lainnya (tungsten diselenide dan tungsten disulfide), menghasilkan transistor vertikal tipe-p dan tipe-n sub-3-nm.

Namun harus dijelaskan bahwa ini hanya produk laboratorium, dan jika benar-benar akan diproduksi massal dan menuju ke bengkel produksi untuk batch pabrik produksi massal mungkin masih memakan waktu lama.

AS Mengundang Tiongkok Bekerjasama Untuk Chip Ini

Setelah itu, pada September 2021, ketika ada berita bahwa Tiongkok dan AS akan bekerja sama di bidang chip muncul, semua orang jadi terkejut.

Semua orang tahu terakhir ini sejak perang iptek, AS sangat ingin memburu dan membunuh semua perusahaan chip Tiongkok.

Dalam setahun terakhir, AS tidak hanya menolak untuk bekerja sama dengan Tiongkok, bahkan tidak mengizinkan negara lain untuk bekerja sama dengan Tiongkok, dan memblokir teknologi chip Tiongkok.

Jadi mengapa AS memilih untuk bersama-sama mengembangkan teknologi dengan Tiongkok di bidang chip kali ini? Itu sangat jelas dan sederhana karena akan menguntungkan bagi AS.

Untuk lebih mengetahui alasannya marilah kita coba mengetahui teknologi yang dikembangkan ini, serta bersama-sama menelaah beberapa konsep dari teknologi ini.

Pertama-tama, perlu kita mengetahui apa itu EDA (Electronic Design Automation)?

EDA adalah teknologi desain sirkuit terintegrasi yang mengintegrasikan teknologi elektronik modern, teknologi komputer, dan teknologi cerdas. Sederhananya, EDA menggunakan semua teknologi mutakhir yang tersedia untuk merancang sirkuit terintegrasi (IC) yang canggih.

Saat ini, desain chip di seluruh dunia didasarkan pada konsep desain EDA dan alat desain EDA.

Lalu apa itu teknologi 3D IC EDA?

Sesuai dengan namanya, tidak lagi terbatas pada desain sirkuit satu lapis ketika sirkuit terintegrasi (IC) digunakan, dan desain sirkuit multi-lapisan dapat dilakukan pada saat yang bersamaan. Alih-alih melakukan desain berlapis satu per satu.

Keuntungan dari teknologi ini pertama dapat menghemat aliran proses dan waktu desain, prosedur desain chip, dan kedua menghemat modal dan biaya yang dikeluarkan dalam mendesain chip.

Tentu saja, poin terpenting adalah teknologi ini dapat melengkapi desain chip yang terintegrasi.

Hal ini sangat mungkin karena teknologi ini akan secara langsung memungkinkan Tiongkok untuk tidak lagi membutuhan mesin litografi, yang secara langsung untuk menghasilkan chip.

Dengan cara ini, Tiongkok dapat sepenuhnya menghindari blokade mesin litografi dari luar negeri.

Sedangkan, alasan mengapa AS ingin bekerja sama dengan Tiongkok untuk mengembangkan teknologi ini pertama-tama karena teknologi ini merupakan teknologi yang sangat menjanjikan.

Dan Tiongkok memiliki teknologi canggih dalam teknologi ini, jika AS bekerja sama dengan Tiongkok, itu dapat sangat mempersingkat siklus penelitian dan pengembangan teknologi ini.

Pada saat yang sama, juga dapat mengurangi banyak pengeluaran yang tidak perlu Sederhananya, kerja sama dengan Tiongkok untuk teknologi ini dapat membawa keuntungan besar bagi AS.

AS seperti rubah tua yang cerdik yang ingin menggunakan teknologi Tiongkok untuk membantu dirinya sendiri membuat terobosan teknologi.

Kedua, Tiongkok memiliki teknologi yang relatif inti dalam penelitian dan pengembangan teknologi ini, dan tidak mungkin bagi AS untuk dapat menyelesaikan penelitian dan pengembangan teknologi ini secara mandiri tanpa Tiongkok.

Oleh karena itu, ini merupakan tindakan yang dikarenakan ketidak berdayanya bagi AS maka mau dan minta untuk bekerja sama dengan Tiongkok. Dalam penelitian dan pengembangan teknologi ini, Tiongkok memegang struktur transistor yang ditangani oleh Universitas Hunan. Teknologi ini dapat membantu teknologi IC EDA 3D menembus serangkaian kemacetan teknis dan memastikan keberhasilan penelitian dan pengembangan teknologi berjalan lancar.

Sehubungan dengan itu, AS mempertimbangkan harus melakukan kerja sama yang mendalam dengan Tiongkok. Pada akhirnya, tujuan AS mungkin sebenarnya ingin mengambil teknologi dari Tiongkok melalui kerja sama ini dan mengambil teknologi canggih Tiongkok.

Namun tampaknya tidak mungkin bagi Tiongkok untuk tidak melihat upaya yang begitu jelas dari AS. Karena seperti kita semua tahu bahwa niatan AS untuk kerjasama terlihat sangat tidak murni, tapi mengapa Tiongkok tetap setuju untuk bekerja sama?

Kerja sama ini jelas terlihat merupakan kerja sama, tapi intinya bukan hanya sekedar kerja sama namun ada strategin permainan pertarungan dan transaksi.

Pertama-tama, sudah diketahui masih ada kesenjangan tertentu antara Tiongkok dan AS dalam hal teknologi EDA, kali ini Tiongkok juga dapat memperoleh banyak teknologi dan pengalaman utama dari AS yang kondusif untuk menembus kemacetan untuk teknologi EDA.

Baik dalam segi posisi strategis maupun masalah kesulitan teknis dalam EDA telah menjadi pertimbangan seksama bagi Tiongkok. Dan teknologi EDA memiliki posisi lebih besar dalam hal ini, Oleh karena itu, meskipun itu adalah pertukaran teknologi, tapi dipandang tidak merugikan Tiongkok.

Kedua, semua teknologi utama dikembangkan secara independen oleh tim Tiongkok, dan dalam realitanya masih ada banyak batasan-batasan teknis dan hambatan teknis yang tetap masih dipegang pihak Tiongkok.

Mungkin tidak mudah bagi pihak AS untuk belajar dengan cepat akan hambatan dan kesulitan ini, sebaliknya Tiongkok akan memperoleh kekuatan tertentu di bidang EDA.

Maka dalam situasi begini, laju kemanjuan dan ruang perbaikan Tiongkok akan lebih cepat daripada AS.

AS mungkin tidak dapat memanfaatkan permainan ini, yang terpenting adalah struktur transistor vertikal dan teknologi yang relevan lainnya oleh Tiongkok telah diajukan hak patennya.

Bahkan jika AS ingin menggunakannya, mereka harus membayar biaya paten, tentu saja, yang terpenting adalah Tiongkok sangat membutuhkan teknologi ini untuk menerobos blokade mesin litografi.

Selama bisa menembus blokade mesin litografi, nilai pembayaran dan pengorbanannya masih bisa diterima. Yang utama Tiongkok harus menjadi penerima manfaat lebih besar dalam kerja sama ini.

Kali ini, AS mungkin akan "gagal", terlepas dari apakah undangan kerja sama AS itu tulus atau munafik, namun pihak Tiongkok tampaknya sudah waspada.

Tampaknya Tiongkok tidak coba mengelak untuk kerja sama kali ini, karena bagaimana pun Tiongkok memegang teknologi inti dalam teknologi ini.

Saat ini, kesenjangan teknologi antara Tiongkok dan AS sudah tidak terlalu besar sehingga AS tidak bisa seenaknya mendominasi Tiongkok.

Kerja sama antara kedua pihak ini hampir merupakan pertukaran teknis yang setara, dalam hal ini Tiongkok memiliki kekuatan yang cukup untuk melindungi keamanan teknisnya sendiri.

Angan-angan AS yang berharap dapat memperoleh keuntungan lebih besar, tampaknya akan meleset.

Sumber: Media TV dan Tulisan Luar Negeri

https://www.nature.com/articles/s41928-021-00566-0

Follow Instagram @kompasianacom juga Tiktok @kompasiana biar nggak ketinggalan event seru komunitas dan tips dapat cuan dari Kompasiana. Baca juga cerita inspiratif langsung dari smartphone kamu dengan bergabung di WhatsApp Channel Kompasiana di SINI