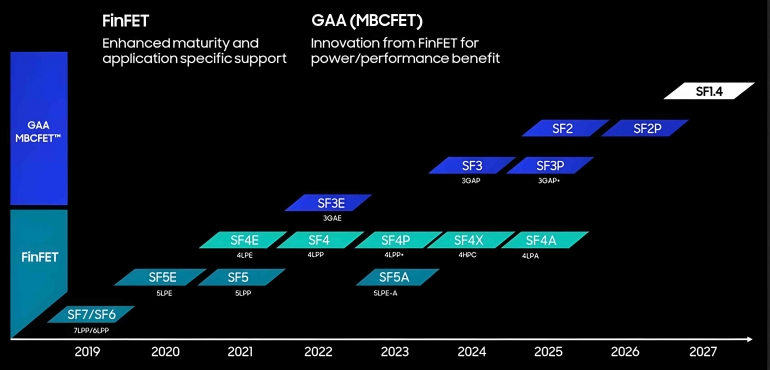

Samsung Foundry adalah perusahaan pembuat chip pertama di dunia yang mengadopsi transistor baru Gate-All-Around (GAA) yang mereka sendiri menyebutnya Multi-Bridge-Channel Field Effect Transistor (MBCFET) yang diimpelentasikan di fabrikasi SF3E (3nm), selanjutnya Samsung akan memperkenalkan teknologi Backside Power Delivery Network yang akan dipakai di fabrikasi SF2 (2nm), menurut laporan dari Chosun.com.

Dalam laporan tersebut mengklaim bahwa hasilnya menjanjikan yang diperoleh dengan teknologi penyaluran daya bagian belakang/Backside Power Delivery yang menyebabkan Samsung memikirkan kembali penerapan Backside Power Delivery Network (BSPDN) . Samsung diduga berencana untuk memperkenalkan Backside Power Delivery Network (BSPDN) di fabrikasi SF1.7 (1,7nm) tetapi mereka mempertimbangkan ulang dan akan memperkenalkannya di fabrikasi 2nm (SF2) yang dijadwalkan pada tahun 2025 berdasarkan Roadmap perusahaan. Namun ada kendala besar dalam laporan ini: peta jalan publik Samsung saat ini tidak menyertakan node kelas 1,7nm dan hanya berisi teknologi SF2, SF2P, dan SF1.4.

Samsung telah berhasil menerapkan teknologi penyaluran daya bagian belakang/Backside Power Delivery pada dua chip uji berbasis Arm, yang menghasilkan pengecilan area cetakan sebesar 10% dan 19%, seperti yang diungkapkan dalam makalah perusahaan yang dipresentasikan di Simposium VLSI pada pertengahan 2023. Teknologi ini biasanya memungkinkan penggunaan kabel yang lebih tebal dengan resistansi yang lebih rendah, sehingga dapat mengalirkan daya yang lebih besar untuk meningkatkan kinerja dan efisiensi daya. Makalah tersebut mencatat bahwa teknologi ini menghasilkan penurunan panjang kabel sebesar 9,2%, yang berkontribusi pada peningkatan kinerja. Selain itu, makalah tersebut menunjukkan bahwa teknologi ini memberikan berbagai manfaat, termasuk peningkatan Fmax sebesar 3,6%, pengurangan area blok standar sebesar 2,4%, dan peningkatan kinerja blok standar sebesar 1,6%. Pekerjaan ini bukan merupakan bagian dari kolaborasi berkelanjutan Samsung dan Arm.

Jika laporan tersebut akurat, maka penerapan Backside Power Delivery Network (BSPDN) ke node SF2 akan membuat teknologi pemrosesan jauh lebih kompetitif dibandingkan teknologi fabrikasi Intel 20A pada tahun 2024 dan Intel 18A pada tahun 2025, serta proses N2P TSMC pada tahun 2026-2027.

Sementara itu, tidak adanya BSDPN di SF3 dan SF3P tentu akan membatasi kinerja, daya, dan kepadatan transistor dari node ini dibandingkan dengan pesaingnya. Meskipun performa puncak yang lebih rendah, daya, dan kepadatan transistor yang lebih rendah mungkin bukan merupakan kerugian besar bagi beberapa desain.

Baca konten-konten menarik Kompasiana langsung dari smartphone kamu. Follow channel WhatsApp Kompasiana sekarang di sini: https://whatsapp.com/channel/0029VaYjYaL4Spk7WflFYJ2H

![[Novel] Menapak Jejak di Kimaam, Episode 41-42](https://assets-a2.kompasiana.com/items/album/2024/11/02/cover-novel-2-6726070c34777c6ffe31bf12.png?t=t&v=100&x=100&info=meta_related)