TSMC dalam pengenalan kemasan canggih 3D di situs resminya, mengatakan bahwa analisis data besar komputasi awan (cloud computing), pelatihan jaringan saraf, penalaran kecerdasan buatan, komputasi seluler pada ponsel cerdas, dan bahkan mobil yang dapat mengemudi sendiri mendorong komputasi hingga batasnya.

Dihadapkan dengan persyaratan aplikasi komputasi yang lebih beragam, teknologi pengemasan canggih telah menjadi jalur inovasi utama untuk terus mengoptimalkan kinerja dan biaya chip.

Pada tahun 2011, TSMC memprakarsai ide memasuki bidang pengemasan semikonduktor, dan kemudian teknologi pengemasan tingkat wafer dikembangkan satu demi satu, dan diadopsi oleh pelanggan seperti Nvidia, Google, dan Fuyue Supercomputer Jepang.

Ketika raksasa industri semikondktor fokus pada proses manufaktur canggih dan persaingan teknologi seperti EUV, pengemasan dan pengujian yang sederhana telah menjadi senjata besar bagi TSMC untuk menyingkirkan Samsung dan Intel.

Pada bulan September 2021, TSMC meluncurkan teknologi pengemasan lanjutan barunya, teknologi integrasi heterogen COUEPE untuk pasar pusat data, sebagai perusahaan terkemuka di pasar pengemasan tradisional.

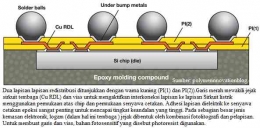

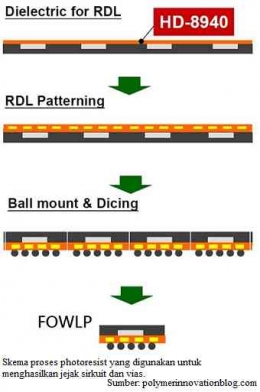

Menghadapi tren pengembangan chip yang heterogen, ASE* juga terus menambahkan teknologi FOWLP* tingkat wafer untuk meningkatkan kekuatannya di bidang pengemasan tingkat lanjut.

*(Fan-out wafer-level packaging (FOWLP) adalah pendorong utama dalam peralihan industri dari penskalaan transistor ke penskalaan dan integrasi sistem.

ASE adalah yang terbesar dari Tiga Besar OSATs-penyedia perakitan dan pengujian semikonduktor outsourcing. Perusahaan ini didirikan pada tahun 1984 dan menyediakan kemasan tingkat wafer fan-out, kemasan skala chip tingkat wafer, flip chip, 2.5D, 3D, sistem-dalam-paket dan ikatan kawat tembaga.)

Meskipun tidak banyak perbedaan antara Samsung dan TSMC dalam hal proses manufaktur, ada kelemahan tertentu di bidang pengemasan, berdasarkan ketertinggalan dalam teknologi pengemasan FOPLP dan FOWLP. Samsung dapat mempersempit kesenjangan mengingat status peningkatan kemasan canggih, Intel juga meletakkan di bidang kemasan 2.5D, dan meluncurkan teknologi jembatan interkoneksi multi-chip tertanam pada tahun 2017, diikuti oleh teknologi kemasan 3D baru yang disebut Foveros pada Desember 2018. .

Teknologi Foveros Intel memanfaatkan kemampuan pengemasan tingkat wafer untuk menyediakan solusi susun 3D yang pertama di jenisnya.